这次Pura70系列除了标准版之外,其它三款机型皆搭载了全新的处理器麒麟9010。单看处理器型号的话,结合以往麒麟处理器命名的规则,一般会认为这就是个麒麟9000S的超频版。

结果处理器的CPU规格一出来,却显示大核主频大幅降低了!至于中核与小核的主频,则是略微提升了一点点,此外其也具备和麒麟9000S一样的超线程设计。

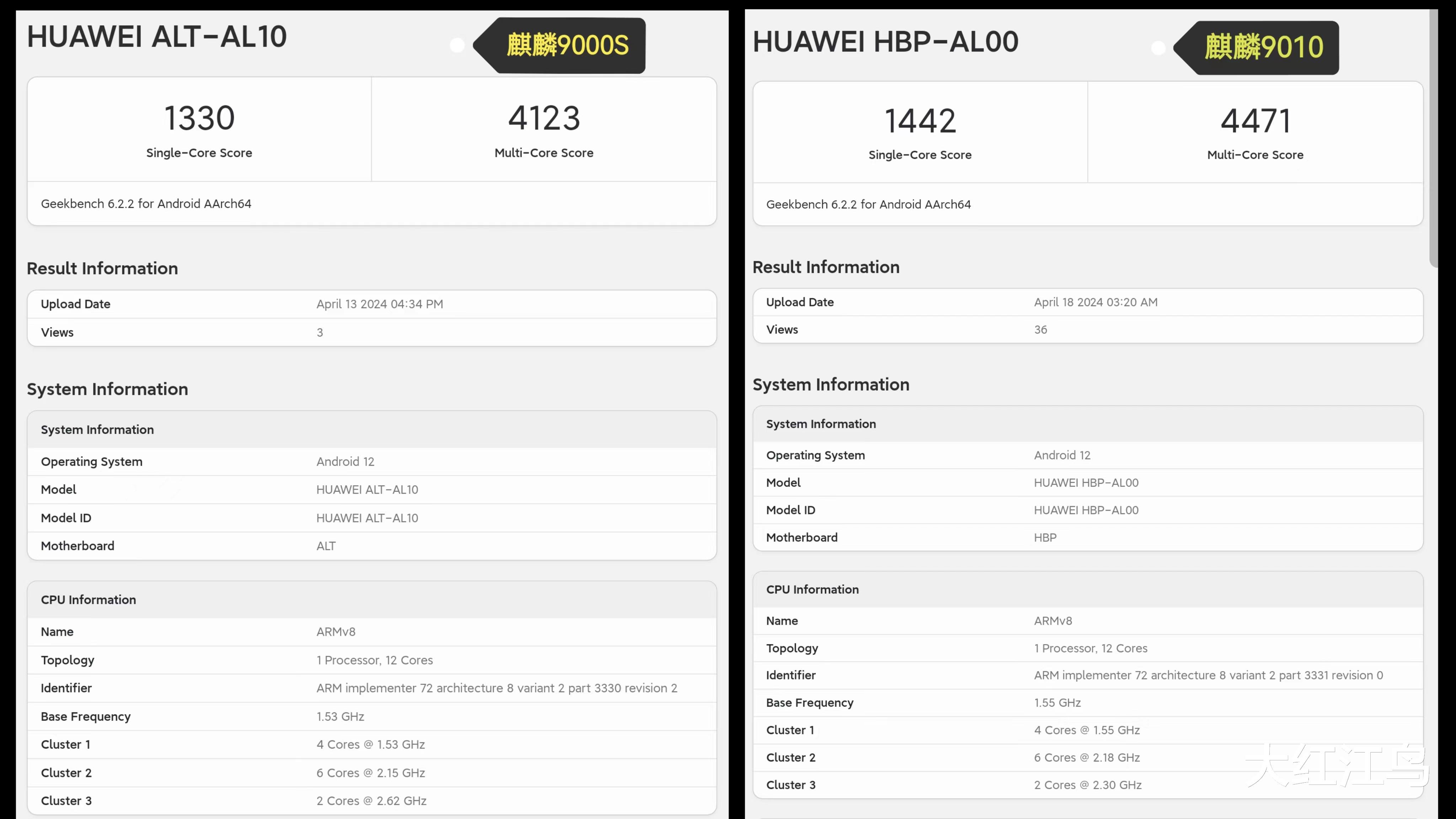

GPU部分则依然是麒麟9000S所采用的那款 Maleoon 910,所以这代唯一的变化就是CPU部分。通过CPU性能的跑分可知(下图所示),大核主频虽然降低了,但性能却上升了!

很明显这并非麒麟9000S的降频版,而是CPU核心微架构得到升级的一款全新处理器!GB6跑分中CPU单核性能上升了8.4%,多核性能也同样是提升了8.4%。

也就是说单看GB6跑分的话,麒麟9010的大核IPC是有23%之提升的,下面再看其大核的整数和浮点跑分之IPC有何变化。

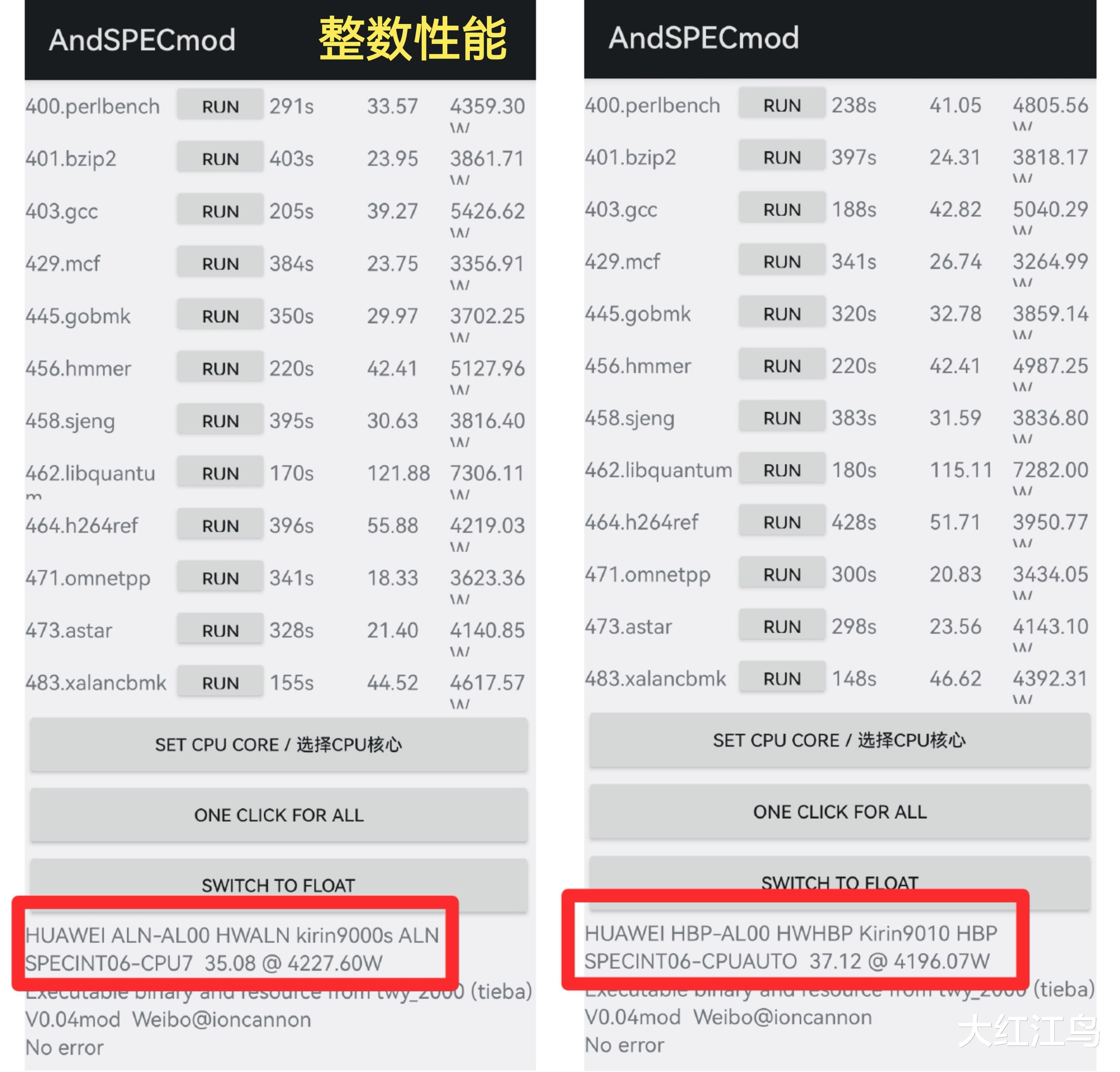

如下图所示,麒麟9010较麒麟9000S的大核整数性能,在相同功耗情况下有5.8%的优势,换言之其能效更高些;若再结合两者主频的区别,就意味着其整数IPC进步了20%!

下图的大核浮点性能部分,麒麟9010较麒麟9000S具有7.25%的优势,而且功耗表现也很一致——能效方面提升明显;结合两者主频的区别,其浮点IPC就进步了21.7%。

总结就是,这次麒麟9010的CPU大核IPC性能,较麒麟9000S是有20%以上之大幅提升的。而且因为频率定得比较低,所以其能效表现较麒麟9000S也有5%以上的提升。

从这也可以看出,在制程工艺受限制的情况下为了改善CPU能效表现,华为想出了微架构大幅升级但却降低主频的办法,最终在相同功耗表现下做到了性能有所提升。

之前麒麟9000S的CPU大核,在IPC性能方面整体是略弱于骁龙888的;而这次麒麟9010的CPU大核,其整数IPC与骁龙8+ Gen1一致,而在浮点IPC上则实现了超越!

也就是说这次麒麟9010的CPU自研大核微架构,在性能设计方面是比较接近骁龙8+ Gen1之X2超大核微架构的,下面就从微架构方面去探究两者有什么相似性。

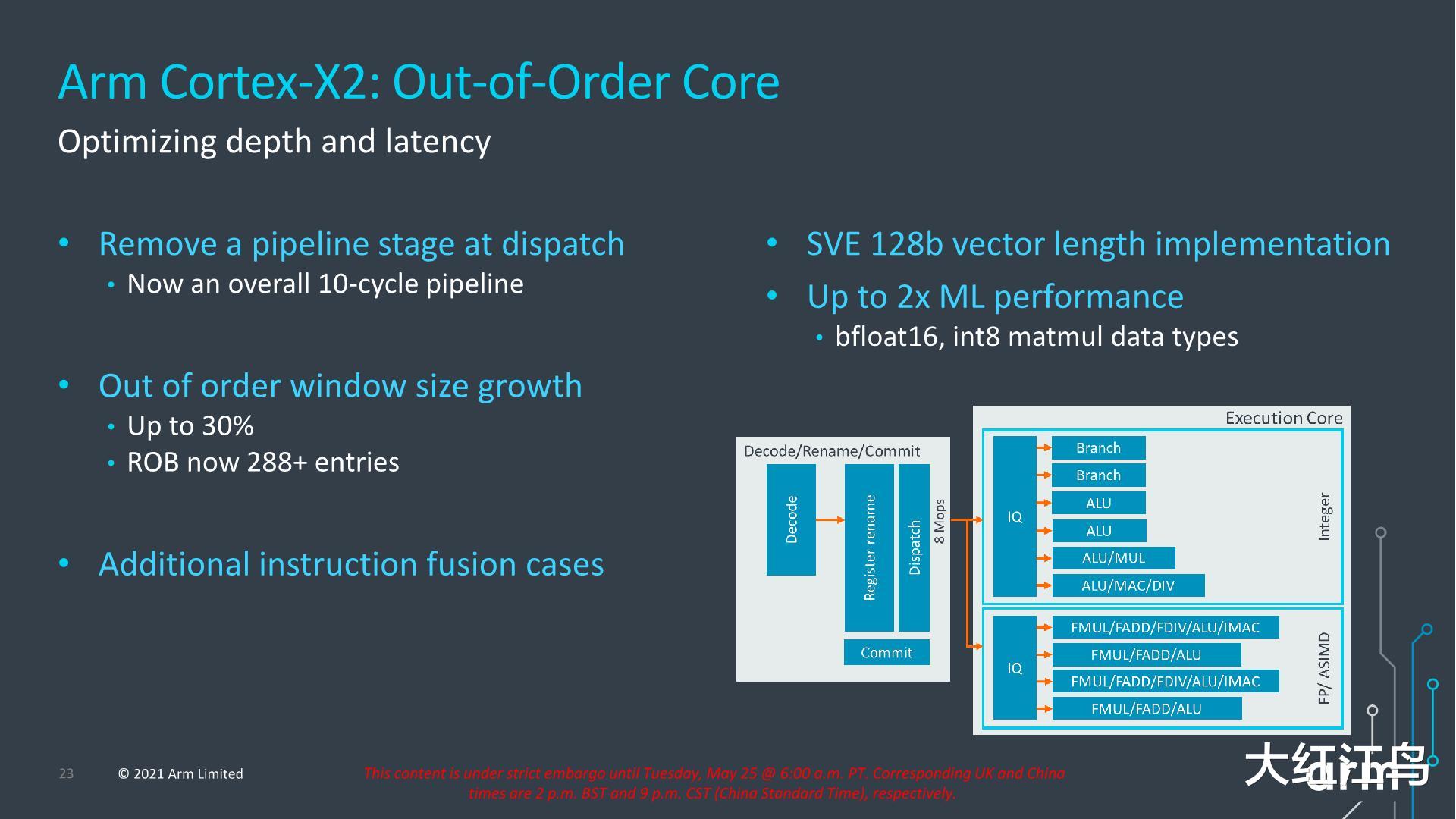

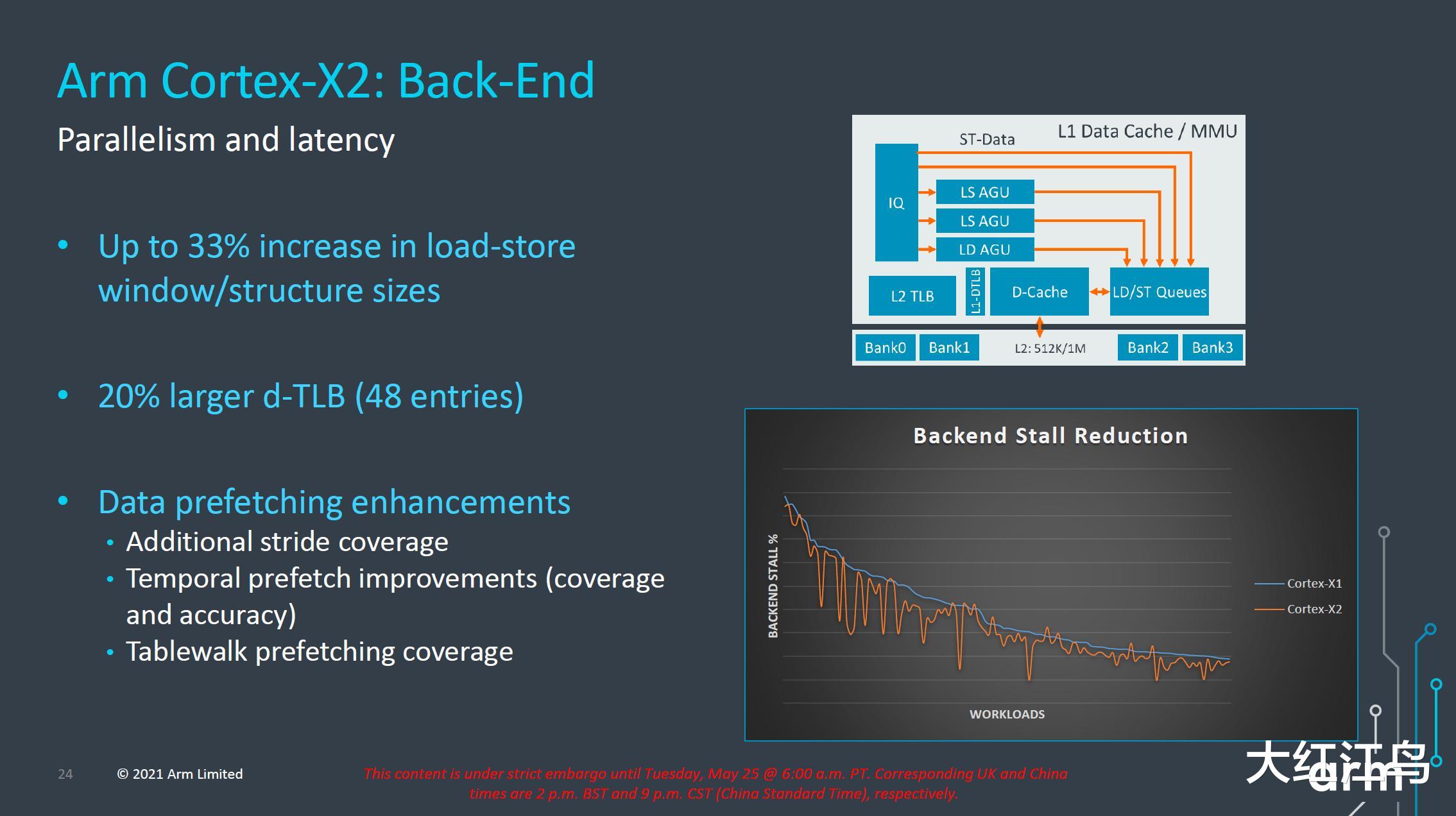

先从Cortex-X2架构入手,从下图可知其前端为8发射宽度,乱序窗口的ROB深度为288,后端整型部分拥有4个整数执行单元,流水线管道从X1的11级减少到了10级。

至于麒麟9010的大核微架构,从已知的信息来看,其与X2微架构只有8发射对得上;其它的诸如8解码宽度、6个整数执行单元,都要大于X2的6解码宽度和4整数执行单元。

另外在缓存系统方面麒麟9010和骁龙8+ Gen1也很像,两者在前端L1指令缓存、后端L1数据缓存、L2缓存等方面皆保持一致,但在L3缓存和SLC缓存等方面麒麟9010还没有确切数值。

由于L3缓存和SLC缓存影响的主要是大核的能效表现,所以在缓存系统方面两者算是把变量控制住了;也就是说,在前端和后端都更宽的情况下,麒麟只有浮点IPC超越了X2。

之所以会出现这种情况,其根因还是与制程工艺有关。另外,说到这就要将微架构的方向看到果子那边了,因为华为在新麒麟的微架构设计路线上,与果芯路线不谋而合。

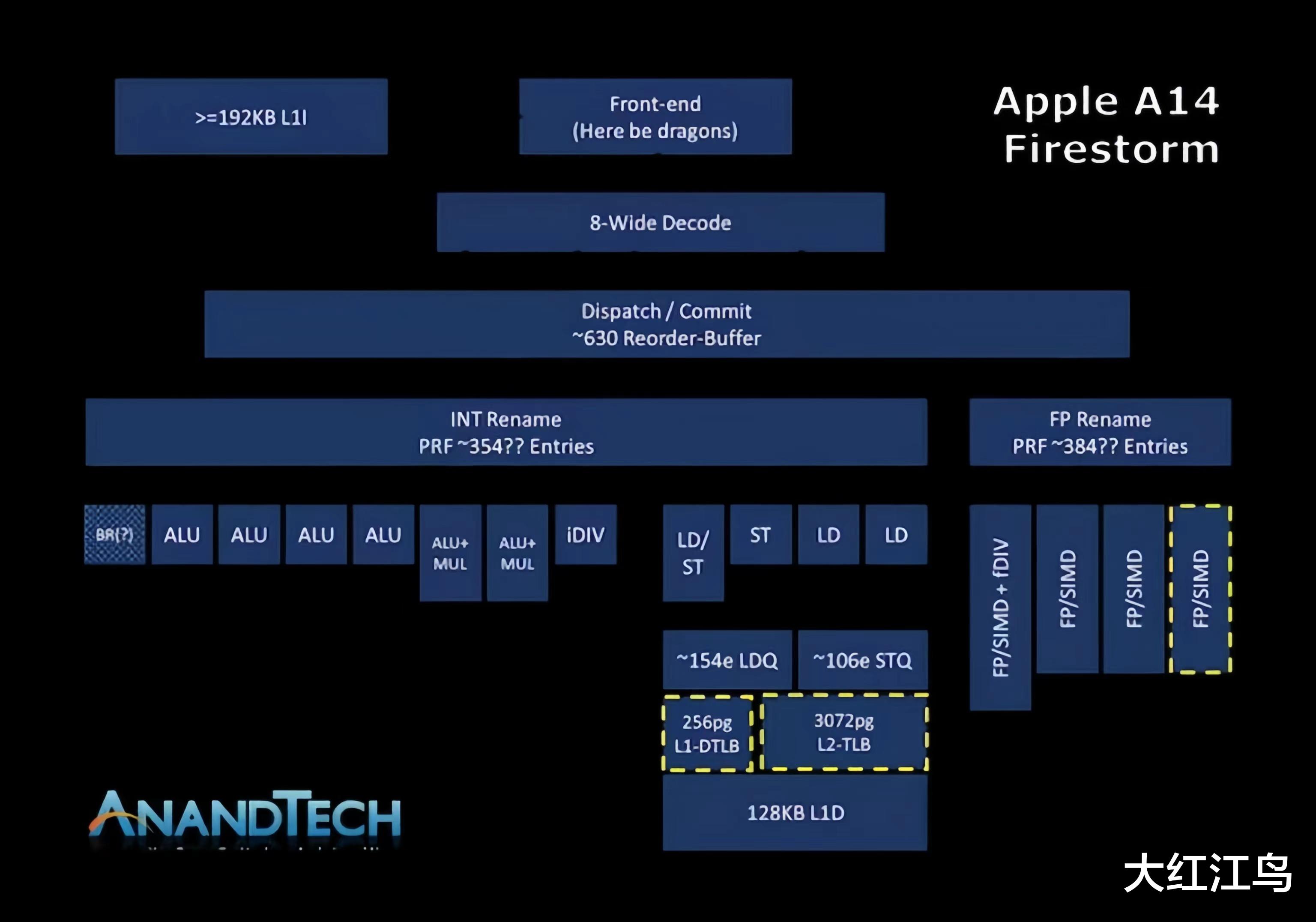

例如麒麟9010大核的8解码8发射前端宽度,与苹果A14的前端宽度一致,同时两者后端的整数单元数量也一样为6个。但是,果子那边缓存系统整体优势极大,且ROB深度高达630!

最终,A14的大核整数IPC性能,比麒麟9010的大核高出了31%!所以,前端后端的宽度只是一个前提,若要顺利实现更好的指令级并行性,还得学果子将该堆的料全都堆上。

最后,还得回到一切的症结所在:制程工艺受限制情况下,华为的微架构设计能力受到严重制约,为了在性能和能效之间保持一个平衡,最终才有了麒麟9010的CPU架构现状。

例如,假如华为要学果子将缓存系统和ROB深度堆上去,那就要增加大量的晶体管,但这样做又会推高成本、增加功耗、降低良率。而解决方法只有一个,那就是升级制程工艺。

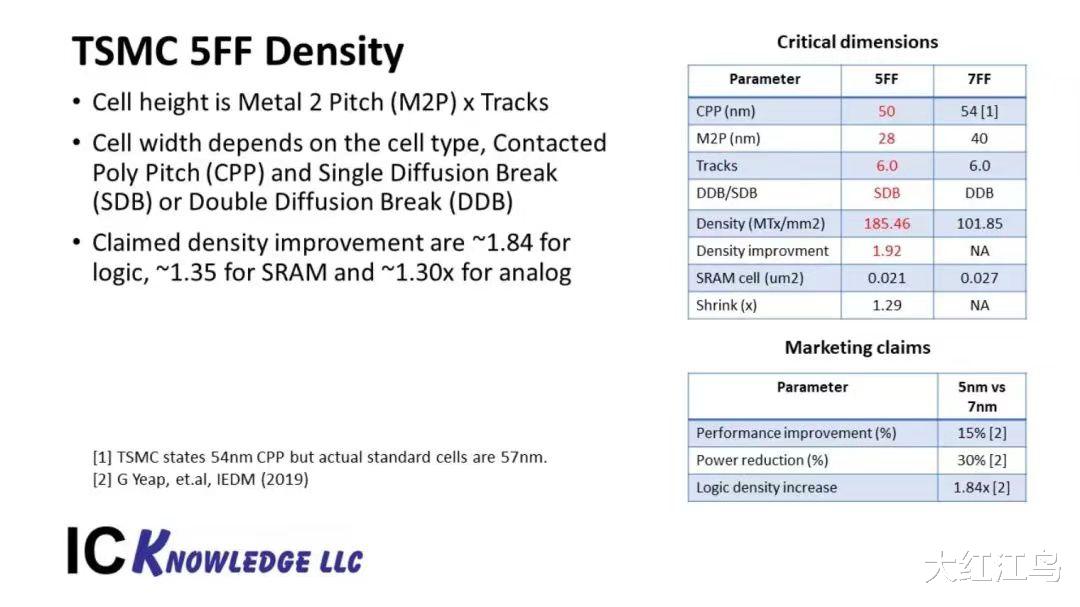

之前在制程升级方面如下图所示,从台积电7nm工艺升级到台积电5nm工艺,可以提高约1.84倍的逻辑密度和1.35倍的SRAM密度,同时还能降低30%的同频功耗,收益极其显著。

其中,提升幅度最大的逻辑密度,可以将SoC内各个功能模块的电路尺寸大幅压缩,这就意味着在相同面积内可以堆更多晶体管,或者在相同晶体管数量下大幅压缩芯片面积。

而SRAM密度则与各级缓存相关,可以在之前同样面积下塞入更大容量的高速缓存;又由于缓存系统与能效表现息息相关,所以这方面堆到位情况下性能设计的余裕空间就很大了。

总的来说这两方面密度大幅提升的结果就是:微架构IPC性能提升的空间极大,因为能够在芯片面积不变或者变小的情况下塞进更多晶体管,其中既有提高性能的也有改善能效的。

解析到这里,麒麟9010大核背靠全新微架构,主频却还是降低至2.3GHz的原因已基本明了,本质上就是制程工艺限制了微架构的设计空间——性能大幅提升与能效表现不可兼得。

假如能有对应的工艺条件,那么麒麟9010的大核微架构就可以像基于台积电5nm工艺打造的苹果A14一样,添加足够的晶体管去堆缓存和ROB,这样便能缩小两者IPC性能的差距。

最后的问题就是,华为和苹果的CPU微架构路线,怎么会不谋而合呢?这其实也挺巧的,华为是迫不得已将电脑端的鲲鹏自研核心延伸至麒麟,而苹果则是从A系列顺延至M系列。

两岸猿声啼不住,轻舟已过万重山!