来源:内容由半导体行业观察(ID:icbank)编译自embedded,谢谢。

过去一年多,生成式人工智能(AI)应用的爆炸式增长刺激了对人工智能服务器的需求,以及对人工智能处理器的需求猛增。这些处理器中的大多数(包括 AMD 和 Nvidia 的计算 GPU、Intel 的 Gaudi 或 AWS 的 Inferentia 和 Trainium 等专用处理器以及 FPGA)都使用高带宽内存 (HBM),因为它提供了当今可能的最高内存带宽。

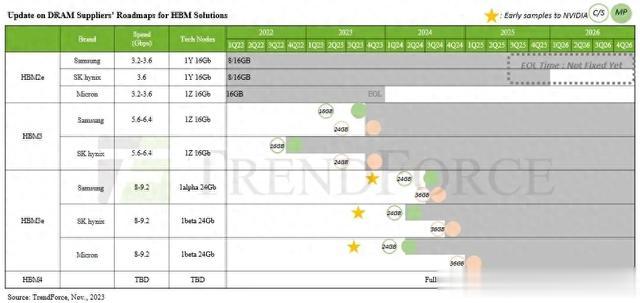

因此,根据TrendForce 的说法,内存制造商美光、三星和 SK 海力士在 2023 年将 HBM 产量提高以后,并在 2024 年进一步提高,例如三星就在最近宣布了扩产计划。

这些承诺将成为业界的挑战。

虽然HBM很不错,但有很多 AI 处理器,特别是那些设计用于运行推理工作负载的处理利用 GDDR6/GDDR6X 甚至 LPDDR5/LPDDR5X 。

此外,还可以给运行 AI 工作负载(针对特定指令进行优化)的通用 CPU 准备使用商用内存,这就是为什么在未来几年我们将看到 MCRDIMM 和 MRDIMM 内存模块将显着提高容量和带宽达到新的水平。

但我们必须强调的是,HBM 仍将保持带宽王者地位。

HBM:不惜一切为带宽

考虑到现代类型内存的性能规格和功能,HBM 在带宽需求大的应用程序中如此受欢迎的原因显而易见。每个堆栈的速度约为 1.2 TB/s,任何传统内存都无法在带宽方面击败 HBM3E。但这种带宽是有代价的,并且在容量和成本方面存在一些限制。

人工智能工程联盟MLCommons的执行董事 David Kanter 表示:“HBM 不仅具有优越的带宽,而且还具有功耗,因为距离很短。” “主要弱点是它需要先进的封装,目前限制了供应并增加了成本。“但 HBM 几乎肯定会永远占有一席之地。”

HBM 的这些特性使得 DDR、GDDR 和 LPDDR 类型的内存也用于许多需要带宽的应用,包括 AI、HPC、图形和工作站。美光表示,这些容量优化和带宽优化类型内存的开发正在迅速进行,因此人工智能硬件开发人员对它们有明确的需求。

美光计算和网络业务部高级经理 Krishna Yalamanchi 表示:“HBM 是一项非常有前途的技术,其市场未来增长潜力巨大。” “目前应用主要集中在人工智能、高性能计算等需要高带宽、高密度、低功耗的领域。随着越来越多的处理器和平台采用它,该市场预计将快速增长。”

有分析人士指出,自 2012 年以来,训练模型以每年 10 倍的速度增长,而且看起来[增长]并没有放缓。”

特别有趣的是,那些需要 HBM 的公司往往会在一夜之间采用该标准的最新版本。

为此Gartner预测,高带宽内存的需求预计将从 2022 年的 1.23 亿 GB 激增至 2027 年的 9.72 亿 GB,这意味着 HBM 位需求预计将从 2022 年占 DRAM 整体的 0.5% 增加到 2027 年的 1.6%这一激增归因于标准 AI 和生成 AI 应用中对 HBM 的需求不断升级。

Gartner分析师认为,HBM收入将从2022年的11亿美元增至2027年的52亿美元,而HBM价格相对2022年的水平将下降40%。Gartner指出,由于技术进步和内存制造商的承诺不断增加,HBM 堆栈的密度也将增加,从 2022 年的 16 GB 增加到 2027 年的 48 GB。与此同时,美光似乎更为乐观,预计在 2026 年左右推出 64 GB HBMNext (HBM4) 堆栈。HBM3 和 HBM4 规范允许构建 16-Hi 堆栈,因此可以使用 16 个 32-Gb 器件构建 64 GB HBM 模块,但这将要求内存制造商缩短内存 IC 之间的距离,其中包括使用新的生产技术。

鉴于 Nvidia 占据了计算 GPU 市场的最大份额,该公司很可能成为业界最大的 HBM 内存消费者,并且这种情况将持续一段时间。

但我们也不得不承认,HBM难度极大。

HBM:太贵了,太难了

生产 HBM 已知良好堆叠芯片 (KGSD) 从根本上来说比生产传统 DRAM 芯片更为复杂。首先,用于 HBM 的 DRAM 设备与用于商用内存(例如 DDR4、DDR5)的典型 DRAM IC 完全不同。内存生产商必须制造 8 或 12 个 DRAM 设备,对其进行测试,然后将它们封装在预先测试的高速逻辑层之上,然后测试整个封装。这个过程既昂贵又漫长。

“HBM 堆栈基于 3D 堆栈 DRAM 架构,该架构使用硅通孔 (TSV) 垂直连接多个芯片,这与商用 DRAM 根本不同,”Yalamanchi 说。“这种带有 TSV 的堆叠架构可实现非常宽的内存接口(1024 位)、高达 36 GB 的内存容量,并可实现超过 1 TB/s 的高带宽操作。DRAM 存储体和数据架构从根本上进行了重新设计,以支持此类并行宽接口。”

这些并不是一个可怕的成本增加因素,这些工具和方法是根据 3D NAND 建立的,您可以通过硅通孔进行连接,所需要做的就是移植现有的 TSV 方法(来自 3D NAND),”DataSecure 首席技术官兼 Boolean Labs 首席技术官兼首席科学家 Michael Schuette说。

但用于 HBM 的 DRAM 设备必须具有宽接口,因此它们的物理尺寸更大,因此比常规 DRAM IC 更昂贵。这也是为什么美光首席执行官 Sanjay Mehrotra 认为,为满足人工智能服务器的需求而增加 HBM 内存产量将影响所有 DRAM 类型的比特供应。

Mehrotra 在早前的电话会议上表示:“高带宽内存 (HBM) 生产将成为行业位供应增长的阻力。” “HBM3E 芯片的尺寸大约是同等容量 DDR5 的两倍。HBM 产品包括逻辑接口芯片,并且具有更加复杂的封装堆栈,这会影响良率。因此,HBM3 和 3E 需求将吸收行业晶圆供应的很大一部分。HBM3 和 3E 产量的增加将降低全行业 DRAM 位供应的整体增长,尤其是对非 HBM 产品的供应影响,因为更多产能将被转移到解决 HBM 机会上。美光Mehrotra 在最近的电话会议上表示:“高带宽内存 (HBM) 生产将成为行业位供应增长的阻力。” “HBM3E 芯片的尺寸大约是同等容量 DDR5 的两倍。HBM 产品包括逻辑接口芯片,并且具有更加复杂的封装堆栈,这会影响良率。因此,HBM3 和 3E 需求将吸收行业晶圆供应的很大一部分。HBM3 和 3E 产量的增加将降低全行业 DRAM 位供应的整体增长,尤其是对非 HBM 产品的供应影响,因为更多产能将被转移到解决 HBM 机会上。”

HBM3E 本质上是具有显着减速的 HBM3,因此虽然 DRAM 制造商必须确保良好的良率,然后调整其生产方法以更有效地构建 8-Hi 24 GB 和 12-Hi 36 GB HBM3E KGSD,但新型内存将并不代表 HBM 生产的重大转变。相比之下,它的继任者将会。计划的 HBM3E 产能提升对我们的位供应能力也产生了类似的影响。”

HBM3E 本质上是具有显著减速的 HBM3,因此虽然 DRAM 制造商必须确保良好的产量,然后调整其生产方法以更有效地构建 8-Hi 24 GB 和 12-Hi 36 GB HBM3E KGSD,但新型内存将并不代表 HBM 生产的重大转变。相比之下,它的继任者将会。

HBM4 将内存堆栈接口扩展至 2048 位,这将是自八年前推出该内存类型以来 HBM 规范最重大的变化之一。对于存储器制造商、SoC 开发商、代工厂以及外包组装和测试 (OSAT) 公司而言,将 I/O 引脚数量增加两倍,同时保持相似的物理占用空间,极具挑战性。三星表示,HBM4 需要从目前用于 HBM 的微凸块键合(这已经很困难且昂贵)过渡到直接铜对铜键合,这是一种用于集成的最先进技术未来几年的多芯片设计。

“如果我看看 [即将推出的 HBM4 规范] 和 2048 位宽接口,这将使引脚数达到约 5500 个引脚,这与大多数服务器 CPU 或 GPU [就引脚数而言] 处于同一水平,”Schuette说。“如果您尝试在小封装设计中布线,最终会得到 20 层重新分布层/中介层之类的东西,如果您选择更大的封装、更少的层数,最终会超过允许的最大走线长度”。

SK 海力士甚至设想 HBM4 必须以 3D 方式集成在片上系统上才能实现最大效率,但这将进一步增加成本。

“在接下来的几年中,我认为我们可能会通过更紧密的集成(例如 3D 堆叠)获得卓越的性能和效率,但这可能会更加昂贵,”Kanter说。

Schuette 认为,由于 HBM4 的引脚数极高,使用具有插入器和重新分配层的传统方法将具有 2048 位接口的 HBM4 堆栈连接到主机处理器可能非常困难。

“最微小的扭曲就会导致连接不良,”Schuette 解释道。“如果它只是一个接地引脚,你可能不会注意到,但如果它是一个信号引脚,你就完蛋了。

但 3D 封装技术将需要更复杂的设备,因此很可能至少在最初只有代工厂自己会在 2025 年至 2026 年的某个时候提供 HBM4 集成。

据报道,为了不断缩小 DRAM 单元尺寸并控制内存功耗,三星打算在 HBM4 中使用 FinFET 晶体管。FinFET 的结合预计将优化即将推出的 HBM 器件的性能、功耗和面积缩放。然而,该技术对成本的影响仍不确定。此外,三星何时在标准 DRAM IC 中采用 FinFET 的时间表尚未确定。目前,三星仅确认 FinFET 将用于 HBM4。

Salvador 表示:“成本问题仍然存在,HBM4 的实施问题可能会延长 HBM3/HBM3E 的使用寿命,特别是在成本更加敏感的地方。”

Yalamanchi 表示:“人们想要采用最快版本的 HBM 并不是一个准确的假设,因为许多因素都会影响内存技术的选择,例如成本、供应限制、平台准备情况和性能要求。”

由于架构和封装成本根本不同,HBM 仍将是一种昂贵的内存类型,服务于不断增长的利基市场。Michael Schuette 部分同意这一观点。他认为,虽然 HBM 很好地服务于其目标市场,但它很难满足更广泛的市场需求。

“HBM 似乎仍然是一种利基产品,并且很可能仍然是一种产品,”Schuette 说。

HBM 能否在成本上与商品或专业内存竞争?

“我不想说永远不会,因为那是一段很长的时间,”Kanter说。“但 HBM 要想具有成本竞争力,就需要大幅降低封装成本和/或显着增加 GDDR 成本。或者可能是根本性的技术转变——例如,如果 GDDR 从高速铜信号转为光纤信号。但我不确定那时是否会是 GDDR。”

LPDDR:低功耗选项

虽然 HBM 在性能方面无与伦比,但对于许多应用来说价格昂贵且耗电,因此开发人员选择将 LPDDR5X 用于其带宽要求较高的应用,因为这种类型的内存为他们提供了价格、性能和功耗之间的适当平衡。

例如,苹果公司多年来一直在其 PC 中使用 LPDDR 内存,然后才成为一种趋势。到目前为止,该公司已经很好地完善了基于 LPDDR5 的内存子系统,其性能是竞争解决方案无法比拟的。Apple 的高端台式机 — 由 M2 Ultra SoC 提供支持的 Mac Studio 和 Mac Pro — 使用两个 512 位内存接口可拥有高达 800 GB/s 的带宽。结合实际情况来看:AMD 最新的 Ryzen Threadripper Pro 配备 12 通道 DDR5-4800 内存子系统,峰值带宽可达 460.8 GB/s。

像苹果一样,在其整个设备系列中使用 LPDDR5 有一些额外的好处,例如 LPDDR5 控制器 IP 和 PHY 在不同的 SoC 中重复使用,以及大量采购此类内存,这为谈判提供了更好的筹码。苹果当然不是唯一一家将 LPDDR 内存用于高带宽处理器的公司。Tenstorrent 将这种内存用于其 Grayskull AI 处理器。

“如今,它们似乎服务于不同的利基市场,并且存在差异化的广泛趋势,”Kanter说。“HBM 更面向数据中心,LPDDR 更面向边缘。话虽如此,绝对有人针对类似的市场使用不同的内存类型。以数据中心为例——有些设计使用 HBM,有些设计使用 GDDR,有些设计使用常规 DDR,有些设计使用 LPDDR。”

LPDDR 存储芯片的显着优势之一是其相对广泛的接口和相当快的运行速度。典型的 LPDDR5 和 LPDDR5X/LPDDR6T IC 具有 32 或 64 位接口,支持高达 9.6 GT/s 的数据传输速率,这比批量生产的 DDR5 数据速率(8 或 16 位、截至 2023 年 10 月,速度高达 7.2 GT/s)更好。此外,移动内存自然比客户端 PC 和服务器的主流 DDR 内存消耗更少的功率。

对于 Tenstorrent 开发的应用程序来说,内存带宽至关重要,但功耗也至关重要,这就是为什么如今 LPDDR 的使用范围远远超出了智能手机和客户端 PC。

GDDR:价格与性能之间的平衡

Tenstorrent 为我们带来了另一种类型的内存,该公司将在即将推出的 Wormhole 和 Blackhole AI 处理器中使用这种内存。与此同时,Nvidia 将 GDDR6 和 GDDR6X 用于各种用于 AI 推理的 GPU。

“GDDR 内存用于人工智能和其他应用,对于人工智能推理应用来说是一个不错的选择,因为 GDDR 仍然提供比 DDR 更高的带宽和更低的延迟,”Yalamanchi 说。“与 HBM 相比,GDDR 的成本更低,复杂性也更低。例如,GDDR6可以在Nvidia用于人工智能推理的Tesla T4 GPU以及用于人工智能推理和图形应用的L40S中找到。”

GDDR6 通常比 LPDDR 消耗更多功率,并且现代 GDDR6/GDDR6X 芯片配备 32 位接口(即比某些 LPDDR5X 更窄),但 GDDR6/GDDR6X/GDDR7 内存的运行速度要快得多。

事实上,GDDR7 有望以高达 36 GT/s 的速度运行,并且在如此高的数据速率下,基于它的内存子系统将比采用 LPDDR5X 的内存子系统快得多,特别是要记住,我们正在谈论潜在的宽内存接口,例如 384 或 512 位。即使在 32 GT/s 数据传输速率下,384 位 LPDDR7 内存子系统也可提供 1,536 TB/s 峰值带宽,远远高于 512 位 LPDDR5X-9600 内存子系统 (614.4 GB/s)。然而,我们可以猜测,LPDDR7 内存子系统也将比使用 LPDDR5X 的内存子系统更加耗电,但考虑到其性能,我们认为这是一个公平的权衡。

MCR-DIMM 和 MR-DIMM

如果没有 MCR-DIMM 和 MR-DIMM,关于高性能内存解决方案的故事就不完整,它们是主要为服务器设计的新型双列 DDR5 内存模块,目前正在开发中。这些技术背后的理念是,在每个 CPU 的核心数量不断增加的情况下,进一步提高内存模块的效率,并将其峰值带宽提高到超过 DDR5 支持的速度。

从较高层面来说,多路复用器组合列 DIMM (MCR-DIMM) 是配备多路复用器缓冲区的双列缓冲内存模块。该缓冲区可以同时从两个队列检索 128 字节的数据,并且它设计为以约 8800 MT/s 的高速与内存控制器配合使用(基于最近发布的美光路线图),即 400 MT/s高于原始 DDR5 规范规定的最大数据速率。这些模块旨在增强性能,同时简化大容量双列模块的构造。MCR-DIMM 得到了英特尔和 SK Hynix 的支持,并将获得英特尔第六代至强可扩展“Granite Rapids”平台的支持,而美光计划于 2025 年初推出 MCR-DIMM。

多列缓冲 DIMM (MR DIMM) 在概念上非常相似:它们是具有多路复用器缓冲区的双列模块,可同时与两个列交互,并以超出 DDR5 指定速度的速度与内存控制器一起运行。该标准的第一代速度为 8,800 MT/s,第二代为 12,800 MT/s,第三代最终达到 17,600 MT/s。该技术得到 JEDEC、AMD、Google 和 Microsoft 的支持。美光计划于 2026 年开始出货速度为 12,800 MT/s 的 MR-DIMM。此类模块将提供巨大的带宽和容量,这是由于数据中心 CPU 内的内核数量不断增加以及对带宽的需求而需要的。

“如果不采用新的形式来实现分类内存,那将是愚蠢的,”Schuette 说。“服务器要求与客户端不同,服务器上始终需要 ECC,而客户端 PC 上则不需要。”

奇异和混合内存子系统

虽然使用特定类型的内存可能是芯片和系统开发人员最明显的做法,但也有人选择使用不同类型内存的混合内存子系统。

例如,英特尔的 Xeon Max CPU 搭载 64 GB 封装 HBM2e,并支持高达 6 TB 的六通道 DDR5 内存,每个插槽最多使用 16 个 DIMM。这些 CPU 主要针对高性能计算 (HPC) 环境,可以在 HBM Only 模式、HBM Flat 模式(提供快速和慢速内存层)和 HBM Caching 模式下工作。

另一个例子是 D-Matrix 的 AI 处理器,内部配备 256 MB SRAM(150 TB/s),并支持高达 32 GB 的 LPDDR5 内存,但带宽相当有限。这些芯片主要用于推理,其架构是针对此类工作负载量身定制的。

“一般来说,缓存或片上 SRAM 可以减少一些外部带宽需求,”Kanter说。“因此,作为推断,如果我们可以接受小于 100MB 的神经网络,[缓存会有所帮助]。同样,我们可以将内存集成得更紧密,以减少封装外带宽。但真正大型培训系统的许多前沿工作,例如训练下一代LLM,总是需要更多带宽。”

虽然历史上由不同类型内存组成的混合和奇异内存子系统已被广泛使用,例如用于 Xbox 360 游戏机的 ATI 的 Xenos GPU 以及基于 eDRAM 的“子芯片”或英特尔的 Xeon Phi 7200-对于同时使用 MCDRAM 和 DDR4 内存的系列协处理器,Schuette 认为此类内存子系统效率不高。

“我的观点是,你会得到两全其美的结果,”他说。“设计开销巨大,复杂性很高,我什至不想进行故障排除。

另一方面,根据定义,所有具有 CPU 和加速器的系统都使用混合内存子系统,并且它们已被证明非常高效。

“如今许多人工智能系统都是混合系统,”Kanter说。“例如,许多训练系统倾向于使用 HBM 作为加速器,但使用 DDR 作为主机处理器,而主机处理器实际上在这里做实际工作。数据中心推理系统也类似。”

综上所述,HBM虽然很好,但一统不了江湖。