在电子应用中,使用两个PMOS管背靠背连接是常见的电路设计,其主要目的是为了提高电路的稳定性和可靠性。

那么,两个PMOS管背靠背连接,是串联还是并联?事实上,两者都是,即存在串联和并联两种方式。今天我们主要带着以下二个核心展开讲解:

串联与并联的电路设计的目的

为什么不能只用一个PMOS?

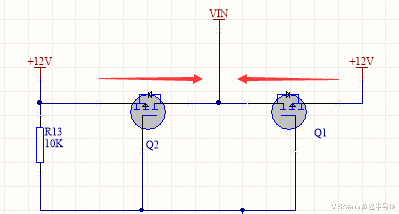

2个PMOS并联,如图

可以看到,当Q1和Q2(PMOS)导通时,左右两边+12V并联增加电流,目的是为了提高VIN(输出端)的带载能力,用来给模块供电。

在这里的两个PMOS管用处就很清楚了:起到分流的作用,因为VIN负载电流会比较大。

在这里对电路设计解释:

控制信号,也就是PHONE_POWER;

当它输出高电平时,三极管Q3导通,两个PMOS Q1和Q2导通,VIN输出端会等于+12V;当它输出低电平时,三极管Q3截止,两个PMOS Q1和Q2截止,VIN输出端会等于0V;

2个PMOS串联,如图

可以看到两个MOS管串联,对电路设计解释:

控制信号,也就是PHONE_POWER;

当它输出高电平时,三极管Q3导通,两个PMOS Q1和Q2导通,VIN输入端会等于VOUT输出端;

当它输出低电平时,三极管Q3截止,两个PMOS Q1和Q2截止,VIN输出端会等于0V;

当需要外接输出端VOUT进行调试时,两个PMOS管进行关闭,可以防止输出端VOUT的电流串到VIN输入端处;如果没有Q1,即输出端VOUT电流从Q2的体二极管串到VIN输入端处。

原理是体二极管的反向截止特性:Q1(左正右负),Q2(左负右正)

那么,为什么不能只用一个MOS管呢?

现在我们来讨论下电路设计:

假设VIN负载最大电流为1A,电路中并联使用两个PMOS,每个PMOS管的IDS电流就会在0.5A以上。

那么问题来了,我们能保证两个管子都是0.5A吗?如果一个是0.7A,一个是0.3A或者一个0.6A,一个0.4A,那其中一个管子不就 因为电流过大而发热甚至导致烧毁?

首先会想到的是,使用两个RDS(on)同样的MOS管,这样流经的电流就会一致了。

但 俗话说得好,这个世界上没有两片完全相同的树叶。MOS管也一样,两个管子同样会存在制造工艺的差异以及其它参数的不一致。

这时候有没有朋友想到我们发过的一期文章?就是MOS管的均流设计。

还是和MOS管的RDS(on)有关,小编看到有朋友是这么说的。

MOS管的RDS(on)和温度是呈正系数关系,即随着温度的升高,RDS(on)会增大。

由于Q1流过的电流会比Q2大,所以Q1的温升肯定比Q2高,这时候Q1的RDS(on)会增大,RDS(on)增大后,流过Q1的电流又会变小,形成一个完整的负反馈,并实现了均流。

不过,想要更保险起见的话,建议选择MOS管时保有余量。比如VIN的最大负载是1A,那么两个PMOS管就可以选择0.6~0.7A的IDS。并且最好选择一致的型号。

这种电路设计的优点,微碧给大家简单的进行了以下整理:

电流共享,避免电流过大损坏器件的风险;

增加开关速度,两个并联能够减小整个电路的开关时间,电阻越小,开关速度越快;

降低电磁干扰,背靠背连接能够减小开关过程中产生的电磁干扰;

提高电路的可靠性,当一个PMOS管出现故障时,另一个PMOS管仍然可以继续工作;

降低成本,选择MOS管时可以在一定程度上降低总成本。

相关的优势与应用分析后面我们有机会再进行探讨!

看到这里的你是否可以点个赞或者关注一下呢!十分感谢您的支持!有什么疑问或者想要探讨的话题可以在评论区一起交流学习噢!

以上部分图片和资料来源于网络