台积电前工程师,胡正明教授在访谈中说到:

到了1nm以后应该怎么去做?我们不要把321这个数字看得太仔细,几纳米这个数字已经没有意义了,只是代表了一个时代而已。这个技术总是会有限度了,我相信在以后的10年之内,我们不单会把晶体管做成三维的,我们甚至会把线路设计成两层三层的,在同一个晶圆上面叠加上去,这个方法可以将晶体管的数目继续增加。

未来的技术方向

未来的技术方向芯片工艺的更新迭代,取决于晶圆内部晶体管的堆叠水平。现在的发展趋势就是在同一个尺寸的晶圆内部,或者尺寸更小的晶圆内部,设计更多的晶体管。

目前最先进的工艺已经发展到了3nm,这些工艺采用的技术手段,还是胡正明教授在1999年开发的Fin FET技术。

这项技术有效的改善了电路控制以及漏电的情况,并且缩短了晶体管的闸长,可以在后来的发展中不断地堆叠更多的晶体管。

这项技术被台积电、三星等国际大厂使用,一直到现在为止,各大厂所量产的先进工艺芯片,依然选择采用这种技术。不过据消息称,三星第二代3nm工艺、未来的2nm工艺,将会使用GAA FET的技术。

GAA FET对比Fin FET,有着更好的控制表现,但是代价也非常大,不但工艺复杂,而且良品率很低。

这项技术现在是台积电和三星争相追赶的技术项目,但是台积电为了求稳,在为苹果代工a17pro芯片的时候,还是选择采用之前的Fin FET技术。

这样虽然良品率高,可以保证出货量,但是在性能的增长、功耗的控制上面,还达不到消费层面的预期,也被许多人称为“挤牙膏”。

三星的情况跟台积电类似,三星掌握GAA FET技术的时间比台积电早半年,但是三星目前为止并,没有将这项技术应用到消费产品上面。

一方面是台积电的工艺比较稳,功耗控制较好,合作商都选择跟台积电合作,另一方面就是三星自己对这项技术还没有信心,自家的Exynos2400芯片,都选择采用了Fin FET技术的4nm工艺。

各企业的发展目前来说,掌握着核心技术的两大代工厂商就是台积电和三星,这两家在晶圆加工领域有着深厚的技术基础。国内发展最好的晶圆企业是中芯国际,但是中芯国际拿不到高端的制造设备,以至于掌握了先进的制程技术,但是没办法进行制造测试。

只能是继续打磨老工艺,或者采用n+1的方式尽可能的增加芯片内部的晶体管数量。

未来的发展趋势必然是晶体管叠加的技术,苹果早在m1 ultra上面就已经进行了测试,将两块m1 max进行封装,重新设计内部的零部件和集成线路,以实现更强性能的芯片叠加技术。

这种技术的优势是可以极大提升性能,劣势则是需要重新进行内部设计,如果设计水平出现了偏差,那么这个产品的功耗就控制不住了。

不过从苹果m1 ultra和m2 ultra这两代产品来看,苹果的设计水平和优化水平已经是行业顶级的水平了,甚至在功耗上面大幅度超过了英特尔和AMD的同期产品。

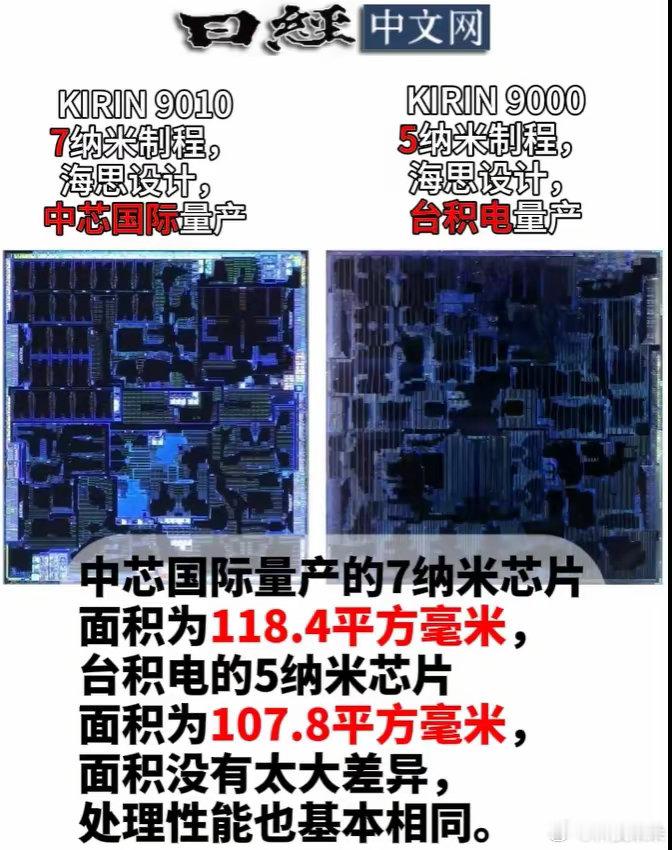

还有就是华为最新的麒麟芯片,在国内外媒体机构的拆解当中,得出结论,麒麟9000s和麒麟9010是等效7nm工艺的芯片。虽然说是等效7nm,但是实际的制造工艺水平达不到7nm的水准。

而且这两款芯片支持超线程,相当于把服务器上面的芯片放在手机上面使用。必须要重新对软件系统进行优化适配,这个技术难度和工作量相当大。也只能是通过这种方式,突破工艺的限制,尽可能地持平产品的性能和功耗。

学华为的堆叠技术[呲牙笑]

吃得不好我们可以多吃点啊,傻编的意思

是小编的👻👻话

以后是以后的事,再说就算堆叠也是3纳米比5纳米堆的多。

堆叠一定能创造出,一个比较烧脑的技术😀