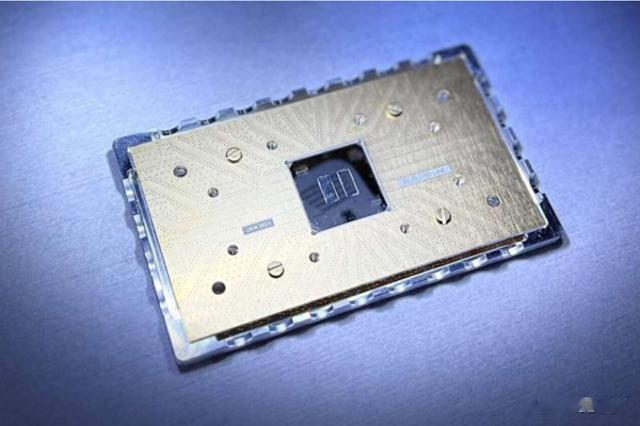

来源:克莱兰实验室

芝加哥大学普利兹克分子工程学院 (UChicago PME) 的研究人员实现了一种超导量子处理器的新设计,旨在为量子革命所需的大规模、耐用设备提供一种潜在的架构。

与将信息处理量子比特放置在 2D 网格上的典型量子芯片设计不同,Cleland 实验室的团队设计了一种模块化量子处理器,包括一个作为中央枢纽的可重构路由器。这使得任何两个量子比特都可以连接和纠缠,而在旧系统中,量子比特只能与物理上离它们最近的量子比特通信。

“量子计算机不一定会在内存大小或 CPU 大小等方面与经典计算机竞争,”芝加哥大学 PME 教授 Andrew Cleland 说。

“相反,它们利用了一种完全不同的扩展方式:将经典计算机的计算能力增加一倍需要两倍的 CPU,或两倍的时钟速度。将量子计算机加倍只需要一个额外的量子比特。

该设计从经典计算机中汲取灵感,将量子比特聚集在中央路由器周围,类似于 PC 通过中央网络集线器相互通信的方式。量子“开关”可以在几纳秒内连接和断开任何量子比特,从而实现高保真量子门和量子纠缠的生成,这是量子计算和通信的基本资源。

“原则上,可以通过路由器连接的量子比特数量没有限制,”芝加哥大学 PME 博士生 Xuntao Wu 说。“如果你想要更多的处理能力,你可以连接更多的量子比特,只要它们适合一定的占用空间。”

Wu 是发表在 Physical Review X 上的一篇新论文的第一作者,该论文描述了这种连接超导量子比特的新方法。研究人员的新型量子芯片具有灵活性、可扩展性,并且与手机和笔记本电脑中的芯片一样模块化。

“想象一下,你有一台经典计算机,它的主板集成了许多不同的组件,比如你的 CPU 或 GPU、内存和其他元素,”Wu 说。“我们的部分目标是将这个概念转移到量子领域。”

大小和噪声量子计算机是高度先进但精密的设备,有可能改变电信、医疗保健、清洁能源和密码学等领域。在量子计算机能够充分发挥这些全球性问题的潜力之前,必须做两件事。

首先,它们必须缩放到足够大的尺寸,并具有灵活的操作性。

“这种扩展可以为传统计算机根本无法解决的计算问题提供解决方案,例如分解大数,从而破解加密代码,”Cleland 说。

其次,它们必须具有容错能力,能够执行大量计算且误差很小,理想情况下要超过当前最先进的经典计算机的处理能力。目前正在开发的超导量子比特平台是构建量子计算机的一种很有前途的方法。

“典型的超导处理器芯片是一个方形,所有量子比特都在其上制造。它是平面结构上的固态系统,“合著者 Haxiong Yan 说,他今年春天从芝加哥大学 PME 毕业,现在在 Applied Materials 担任量子工程师。“如果你能想象一个 2D 阵列,比如一个方形晶格,那就是典型超导量子处理器的拓扑结构。”

典型设计中的局限性这种典型的设计会导致几个限制。

首先,将量子比特放在网格上意味着每个量子比特最多只能与四个其他量子比特交互,即它在北部、南部、东部和西部的直接邻居。更大的量子比特连接通常会在灵活性和组件开销方面实现更强大的处理器,但四邻限制通常被认为是平面设计所固有的。这意味着对于实际的量子计算应用程序,使用残酷的武力扩展设备可能会导致不切实际的资源需求。

其次,最近邻连接反过来会限制可以实现的量子动力学类别以及处理器能够执行的并行程度。

最后,如果所有量子比特都在同一平面衬底上制造,那么这会对制造良率构成重大挑战,因为即使有少量故障设备也意味着处理器无法工作。

“要进行实用的量子计算,我们需要数百万甚至数十亿个量子比特,并且我们需要使一切都完美无缺,”Yan 说。

重新思考芯片为了解决这些问题,该团队对量子处理器的设计进行了润色。该处理器设计为模块化,在安装到处理器主板之前可以预先选择不同的组件。

该团队的下一步是研究将量子处理器扩展到更多量子比特的方法,寻找扩展处理器功能的新协议,并可能找到像超级计算机连接其组件处理器一样链接路由器连接的量子比特集群的方法。

他们还希望扩大可以纠缠量子比特的距离。

“目前,耦合范围是中等范围,大约是毫米级,”Wu 说。“因此,如果我们试图考虑连接远程量子比特的方法,那么我们必须探索将其他类型的技术与我们当前的设置集成的新方法。”

更多信息:Xuntao Wu 等人,具有 All-to-All Reconfigurable Router 的模块化量子处理器,Physical Review X(2024 年)。DOI: 10.1103/PhysRevX.14.041030

期刊信息: Physical Review X